Sub Bab 2.9 Clampers

DAFTAR ISI

Untuk periode t2 → t3 jaringan sekarang akan muncul seperti pada Gambar. 2.98, dengan satu-satunya perubahan tegangan yang melintasi kapasitor. Menerapkan hasil hukum tegangan KirchhoffOutput yang dihasilkan muncul pada Gambar. 2.99, memverifikasi pernyataan bahwa ayunan input dan output adalah sama

5. Prinsip Kerja [kembali]

1. Tujuan [kembali]

- Untuk mengetahui fungsi dari Clampers

- Untuk mengetahui cara kerja Clampers

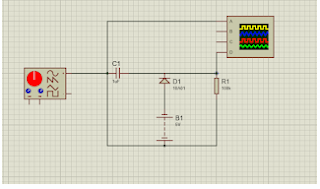

2. Komponen [kembali] Alternator

Alternator merupakan alat yang digunakan untuk mengkonversikan energi mekanik menjadi energi listrik arus bolak-balik (AC).

- Resistor

Resistor adalah komponen dasar elektronik yang berfungsi untuk membatasi atau menghambat aliran listrik yang melewati suatu rangkaian. Dinyatakan dalam satuan Ohm dan dilambangkan dengan Ω (Omega).

Clampers adalah rangkaian yang digunakan untuk melakukan clamp (menggeser) sebuah sinyal ke level dc yang berbeda. clampers merupakan jaringan yang terdiri atas dioda, kapasitor, dan elemen resistif. tetapi juga dapat menggunakan suplai dc independen untuk memasukkan pergeseran tambahan.

Besarnya Rand Cm harus dipilih sedemikian rupa sehingga konstanta waktu RC cukup besar untuk memastikan bahwa tegangan melintasi kapasitor tidak keluar secara signifikan selama antar-val dioda non-konduktor. Sepanjang analisis kami akan berasumsi bahwa untuk semua tujuan praktis kapasitor akan mengisi penuh atau mengosongkan dalam lima konstanta waktu.

Jaringan penjepit memiliki kapasitor yang terhubung langsung dari input ke output dengan a

elemen resistif secara paralel dengan sinyal output. Dioda juga diparalelkan dengan

sinyal output tetapi mungkin atau mungkin tidak memiliki suplai dc seri sebagai elemen tambahan.

.

Jaringan pada Gambar 2.89 akan menjepit sinyal input ke level nol (untuk dioda ideal). Resistor R dapat berupa resistor beban atau kombinasi paralel dari resistor beban dan resistor yang dirancang untuk memberikan tingkat R yang diinginkan. Selama interval 0 → T / 2 jaringan akan muncul seperti yang ditunjukkan pada Gambar 2.90, dengan dioda dalam keadaan "on" secara efektif "menyingkat" efek resistor R. Konstanta RCtime yang dihasilkan sangat kecil (Ditentukan oleh bawaan resistansi jaringan) yang akan diisi kapasitor ke Vvolts dengan sangat cepat. Selama ini tegangan keluaran intervalthe langsung melintasi hubung singkat dan vo = 0 V.

Ketika input beralih ke status = V, jaringan akan muncul seperti yang ditunjukkan pada Gambar. 2.91, dengan rangkaian terbuka ekuivalen untuk dioda ditentukan oleh sinyal yang diterapkan dan tegangan yang disimpan melintasi kapasitor — keduanya "menekan" arus melalui dioda dari katoda ke anoda. Sekarang Ris kembali di jaringan, konstanta waktu yang ditentukan oleh produk RC cukup besar untuk menetapkan periode pelepasan 5 jauh lebih besar dari periode T / 2 → T, dan dapat diasumsikan pada basis perkiraan bahwa kapasitor memegang semua nya mengisi daya dan, oleh karena itu, tegangan (sejak V Q / C) selama periode ini.

Karena vois paralel dengan dioda dan resistor, itu juga dapat digambar dalam posisi al-ternatif yang ditunjukkan pada Gambar. 2.92. Menerapkan hukum tegangan Kirchoff di sekitar loop input akan menghasilkan

Tanda negatif yang dihasilkan dari kenyataan bahwa polaritas 2V berlawanan dengan polaritas yang didefinisikan untuk vo. Bentuk gelombang keluaran yang dihasilkan muncul pada Gambar. 2.92 dengan sinyal masukan. Sinyal output dijepit ke 0 V untuk interval 0 hingga T / 2 tetapi mempertahankan ayunan total yang sama (2V) sebagai input.

Tanda negatif yang dihasilkan dari kenyataan bahwa polaritas 2V berlawanan dengan polaritas yang didefinisikan untuk vo. Bentuk gelombang keluaran yang dihasilkan muncul pada Gambar. 2.95 dengan sinyal masukan. Sinyal output dijepit ke 0 V untuk interval 0 hingga T / 2 tetapi mempertahankan ayunan total yang sama (2V) sebagai input.

Clampers : Ayunan total output sama dengan ayunan total sinyal input.

Fakta ini merupakan alat pengecekan yang sangat baik untuk hasil yang diperoleh. Secara umum, langkah-langkah berikut mungkin berguna saat menganalisis jaringan penjepit:

1. Mulai analisis jaringan penjepit dengan mempertimbangkan bagian sinyal masukan yang akan meneruskan bias dioda.

Pernyataan di atas mungkin memerlukan melewatkan interval sinyal input (seperti ditunjukkan dalam contoh berikut), tetapi analisis tidak akan diperpanjang dengan ukuran investigasi yang tidak perlu.

2. Selama periode dioda dalam keadaan "on", asumsikan bahwa pacitor akan mengisi daya secara instan ke level tegangan yang ditentukan oleh jaringan.

3. Asumsikan bahwa selama periode ketika dioda dalam keadaan "off", pacitor akan mempertahankan level tegangan yang telah ditetapkan.

4. Sepanjang analisis, pertahankan kesadaran yang berkelanjutan tentang lokasi dan polaritas referensi untuk voto memastikan bahwa tingkat suara yang tepat diperoleh.

5. Perlu diingat aturan umum bahwa ayunan total dari total output harus sesuai dengan ayunan sinyal input.

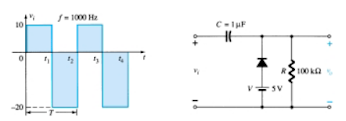

Example 2.22

Tentukan vo untuk jaringan pada gambar 2.93

Perhatikan bahwa frekuensinya 1000 Hz, menghasilkan periode 1 ms dan interval 0,5 ms antar level. Analisis akan dimulai dengan periode t1 → t2 sinyal input karena dioda berada dalam keadaan hubung singkat seperti yang direkomendasikan oleh komentar 1. Interval selanjutnya jaringan akan muncul seperti yang ditunjukkan pada Gambar 2.94. Outputnya melintasi R, tetapi juga langsung melintasi baterai 5-V jika Anda mengikuti koneksi langsung antara terminal yang ditentukan untuk vo dan terminal baterai. Hasilnya adalah vo = 5 V untuk interval ini. Menerapkan hukum tegangan Kirchoff di sekitar loop input akan menghasilkan

Karena itu kapasitor akan mengisi daya hingga 25 V, seperti yang dinyatakan dalam komentar 2. Dalam hal ini resistor Ris tidak disingkat oleh dioda tetapi rangkaian ekuivalen Thévenin dari bagian jaringan yang termasuk baterai dan resistor akan menghasilkan RTh = 0ohm dengan ETh = V = 5 V. Untuk periode t2 → t3 jaringan akan muncul seperti yang ditunjukkan pada Gambar 2.95. Setara sirkuit terbuka untuk dioda akan menghapus baterai 5-V dari tidak memiliki efek apa pun pada vo, dan menerapkan Kirchhoff hukum tegangan di sekitar loop luar jaringan akan menghasilkan

Konstanta waktu dari jaringan pemakaian pada Gambar 2.96 ditentukan oleh RC produk dan memiliki besarannya

Untuk keadaan hubung singkat, jaringan sekarang terlihat seperti Gambar 2.97 dan v0 dapat ditentukan oleh hukum tegangan Kirchhoff di bagian keluaran.Oleh karena itu, waktu pelepasan total 5t = 5 (10 ms) = 50 ms.

Karena interval t2 → t3 hanya akan bertahan selama 0,5 ms, ini merupakan perkiraan yang baik bahwa kapasitor akan menahan tegangannya selama periode pelepasan antara pulsa sinyal input. Output yang dihasilkan muncul pada Gambar 2.99 dengan sinyal input. Perhatikan bahwa ayunan output 30 V cocok dengan ayunan input seperti yang dicatat pada langkah 5.

Example 2.23

Ulangi contoh 2.22 dengan menggunakan dioda silikon VT=0,7 V

Solusi :

Untuk bagian masukan, hukum tegangan Kirchoff akan menghasilkan

5. Prinsip Kerja [kembali]

8. Problems [kembali]

9. Multiple choices [kembali]

37. Sketsa vo setiap jaringan pada gambar 2.181

38. Sketsa vo setiap jaringan pada gambar 2.182

1. Tentukan besar vo

A. 5

B. 15

C. 25

D. 30

E. 35

Komentar

Posting Komentar